RP2040でPIOをプロジェクト新規作成して動かすまで(C言語)

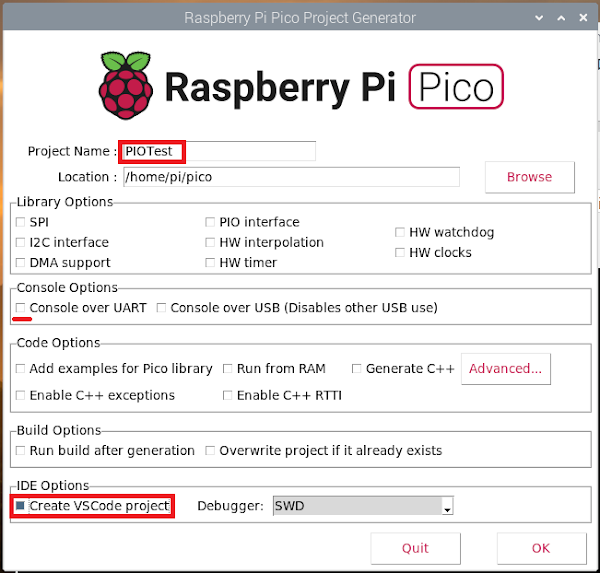

RP2040でPIOを動かすまでのプロジェクト新規作成・ビルド方法について解説します。 ここではPythonではなくC言語をターゲットとしています。 まず、『PIOTest』プロジェクトを プロジェクトの作成 を参考にして作成します。 プロジェクトの作成 を参考に、ビルド・デバッグができる所まで進めたら、VSCodeのエクスプローラーで、PIOTest.cと同一階層にPIOTest.pioというファイルを新規作成し、次のように編集します。(末尾の『%}』 以降に余計な改行等が無いように注意してください) PIOTest.pio .program PIOTest ; TX FIFOから32bitのデータを繰り返し取得し、 ; FIFOが空になるとpullでFIFOにデータが入るまで待機します。 ; また、取得したデータの最下位ビットをあらかじめ設定してある ; 出力ピン(GPIO)に書き込みます。 loop: pull out pins, 1 jmp loop % c-sdk { static inline void PIOTest_program_init(PIO pio, uint sm, uint offset, uint pin) { pio_sm_config c = PIOTest_program_get_default_config(offset); // ステートマシンにてOUTの対象(『out pins, 1』等で値が入る対象)となるGPIOを設定します。 // 変数pinにはGPIO番号が入ります。次の引数にはそのGPIO番号からいくつ連続で使用するかの値で、 // ここでは"1"としていますので、pinのGPIOのみが使用されることになります。 sm_config_set_out_pins(&c, pin, 1); // GPIO番号"pin"をGPIOとして使えるようにします。 pio_gpio_init(pio, pin); // 対象のGPIOを出力に設定します。(true:出力 false:入力) pio_sm_set_consecutive_pindirs(pi...